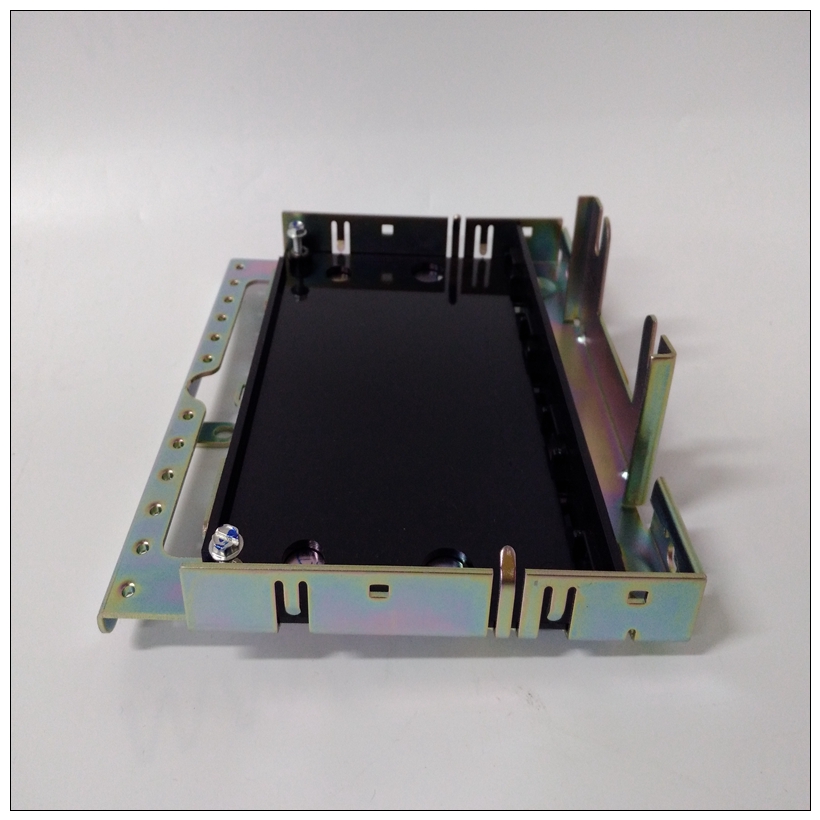

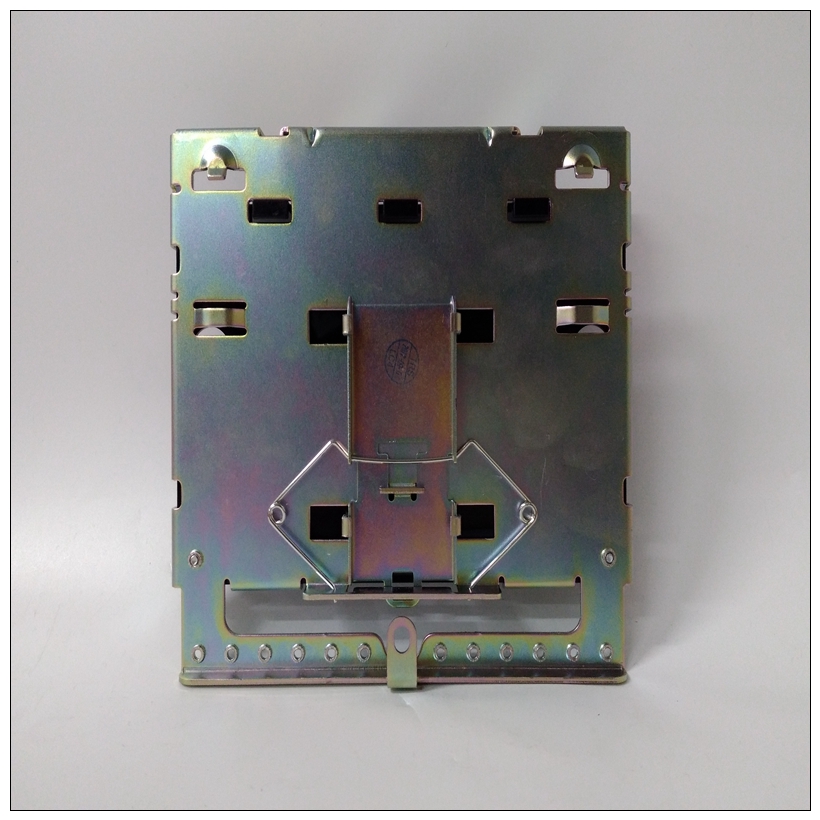

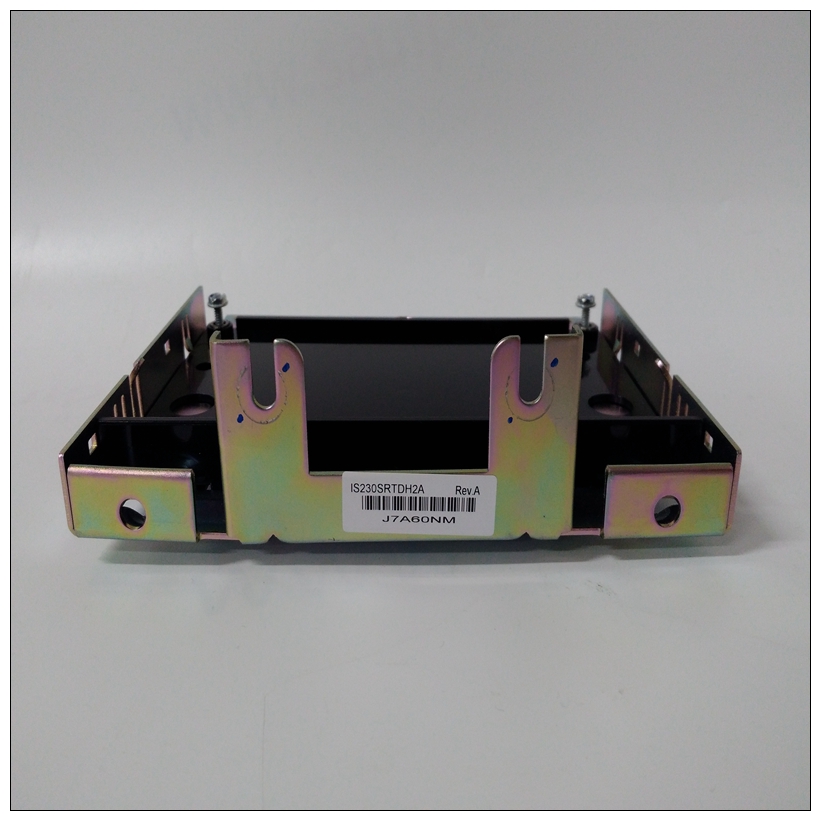

IS230SRTDH2A處理器燃機卡,GE使用參數

這減少了SCSI設備對本地總線的使用。參考MCchipMVME162嵌入式控制器中的編程模型參考指南。在奇偶校驗關閉的情況下,DMA控制器在25 MHz時的傳輸速率為44MB/s以及交錯的DRAM和讀取周期。假設連續傳輸速率SCSI總線上的帶寬為5MB/s,本地總線帶寬的12%用于從SCSI總線傳輸。LAN DMA傳輸MVME162包括與DMA控制器的LAN接口。

IS230SRTDH2A處理器燃機卡局域網DMA控制器使用FIFO緩沖器將串行LAN總線連接到32位本地總線公共汽車FIFO緩沖區允許LAN DMA控制器有效傳輸數據數據傳輸到本地總線。82596CA不執行MC68040兼容的突發周期,因此LAN DMA控制器不使用突發傳輸。奇偶校驗DRAM寫入周期需要3個時鐘周期,讀取周期需要5個時鐘周期,奇偶校驗關閉和奇偶校驗開啟的6個時鐘周期。LAN DMA控制器的傳輸速率在25 MHz時為20MB/s奇偶校驗關閉。假設LAN總線上的連續傳輸速率為1MB/s,本地總線帶寬的5%用于LAN總線的傳輸。遠程狀態和控制遠程狀態和控制連接器J4是一個20針連接器,位于MVME162前面板后面。它為系統設計者提供了訪問關鍵指示器和重置功能的靈活性。這允許系統設計師將構建一個可定位的重置/中止/LED面板從MVME162遠程。介紹如本手冊前幾章所述,MVME162的兩個串行端口(內部端口A,前面板上的串行端口1/控制臺)為EIA-232-D DCE端口專用。第二個端口(端口B內部,串行前面板上的端口2)可以通過串行接口模塊配置為EIA-232-D DCE/DTE或EIA-530 DCE/DTE端口。MVME162使用Zilog Z85230串行端口控制器來實現這兩個功能串行通信接口。每個接口支持CT、DCD、RTS、,和DTR控制信號以及TxD和RxD發送/接收數據信號和TxC/RxC同步時鐘信號。Z85230支持同步(SDLC/HDLC)和異步協議。MVME162硬件支持110B/s到38.4KB/s的異步串行波特率。

This reduces local bus usage by the SCSI device. Refer to the MCchip

Programming Model in the MVME162 Embedded Controller Programmer’s

Reference Guide.

The transfer rate of the DMA controller is 44MB/sec at 25 MHz with parity off

and interleaved DRAM and read cycles. Assuming a continuous transfer rate

of 5MB/sec on the SCSI bus, 12% of the local bus bandwidth is used by

transfers from the SCSI bus.

LAN DMA Transfers

The MVME162 includes a LAN interface with DMA controller. The LAN DMA

controller uses a FIFO buffer to interface the serial LAN bus to the 32-bit local

bus. The FIFO buffer allows the LAN DMA controller to efficiently transfer

data to the local bus.

The 82596CA does not execute MC68040 compatible burst cycles, therefore the

LAN DMA controller does not use burst transfers. Parity DRAM write cycles

require 3 clock cycles, and read cycles require 5 clock cycles with parity off and

6 clock cycles with parity on.

The transfer rate of the LAN DMA controller is 20MB/sec at 25 MHz with

parity off. Assuming a continuous transfer rate of 1MB/sec on the LAN bus,

5% of the local bus bandwidth is used by transfers from the LAN bus.

Remote Status and Control

The remote status and control connector, J4, is a 20-pin connector located

behind the front panel of the MVME162. It provides system designers with

flexibility in accessing critical indicator and reset functions. This allows a

system designer to construct a RESET/ABORT/LED panel that can be located

remotely from the MVME162.Introduction

As described in previous chapters of this manual, one of the MVME162’s two

serial ports (port A internally, SERIAL PORT 1/CONSOLE on the front panel) is

an EIA-232-D DCE port exclusively. The second port (port B internally, SERIAL

PORT 2 on the front panel) can be configured via serial interface modules as an

EIA-232-D DCE/DTE or EIA-530 DCE/DTE port.

The MVME162 uses a Zilog Z85230 serial port controller to implement the two

serial communications interfaces. Each interface supports CTS, DCD, RTS,

and DTR control signals as well as the TxD and RxD transmit/receive data

signals, and TxC/RxC synchronous clock signals. The Z85230 supports

synchronous (SDLC/HDLC) and asynchronous protocols. The MVME162

hardware supports asynchronous serial baud rates of 110B/sec to 38.4KB/sec.