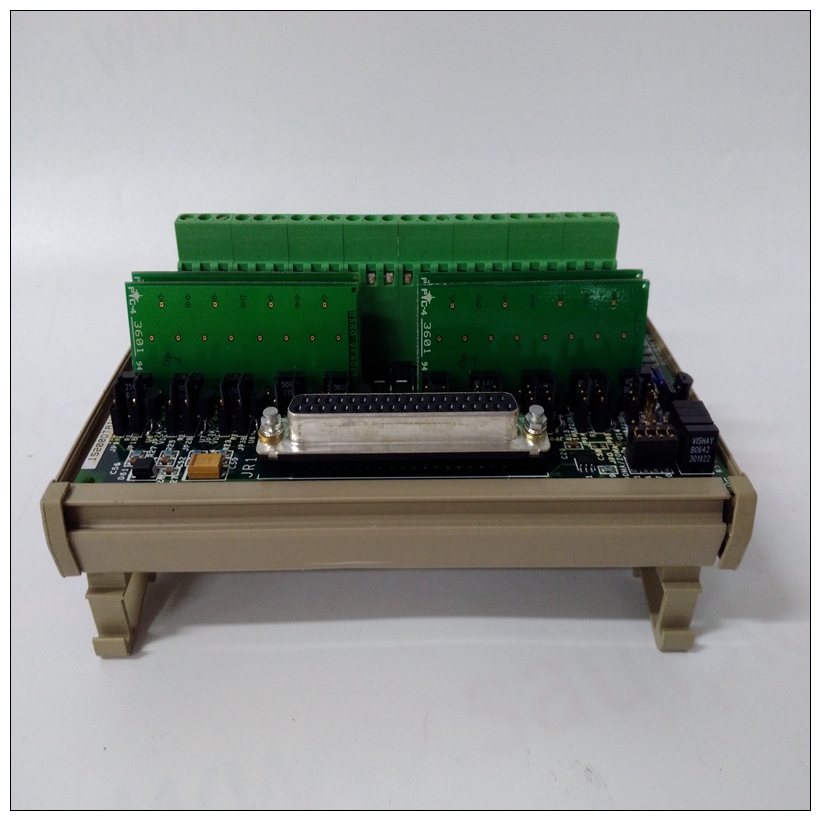

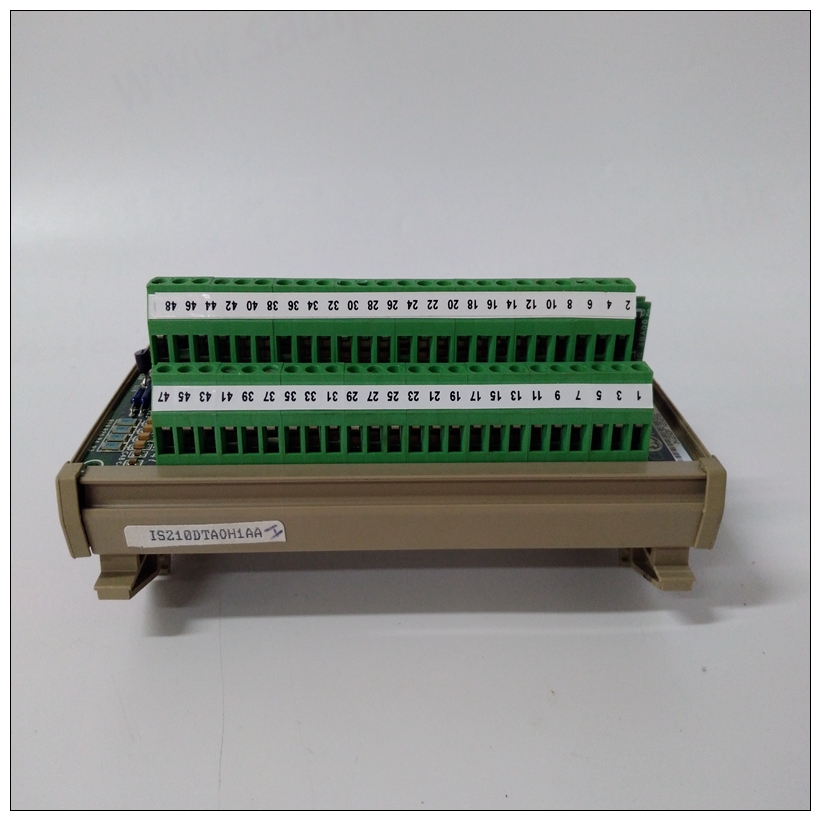

IS200DTAIH1ACC IS210DTAOH1AA燃機模塊,GE使用進展

DRAM可通過MC68030、PCC、LANCE和VMEbus。它專門針對MC68030進行了優化。MVME147-010上未實現奇偶校驗功能。MVME147具有奇偶校驗,在三個用戶中的一個用戶中運行可選模式。在模式1中,不執行奇偶校驗,DRAM工作以最大速度。

在模式2中,對所有總線主機和當MC68030為總線時,DRAM以最大速度運行主人當模式2中出現奇偶校驗錯誤且MC68030為在本地總線主控器中,總線錯誤信號在當前周期。

IS200DTAIH1ACC IS210DTAOH1AA燃機模塊總線錯誤在所有后續事件中激活MC68030 DRAM周期。通知所有其他總線主控器奇偶校驗當前周期中的錯誤,因此其DRAM訪問時間增加1個時鐘。在模式3中,對所有總線主機和在當前周期內報告奇偶校驗錯誤。在這種模式下DRAM訪問時間延長一個時鐘周期,以允許奇偶校驗檢查。

MC68030 DRAM訪問MC68030是默認的本地總線主機,因此它是本地總線總線主控,只要沒有其他設備請求本地總線主控。PCC DRAM訪問當PCC需要傳輸數據時,它請求本地總線GCC多端口仲裁器的主控權。當PCC被授予本地總線主控權后,它執行一個總線周期然后釋放總線主控權。如果在測試過程中檢測到奇偶校驗錯誤PCC到DRAM的讀取周期,總線錯誤返回到PCC。功能描述當VMEbus map解碼器檢測到車載DRAM選擇時,VMEchip從GCC請求本地總線主控多端口仲裁器。當GCC多端口仲裁器已授予本地總線主控,發生DRAM讀寫循環,并且

VMEchip激活DTACK*(或BERR*,如果啟用奇偶校驗,并且VMEbus上出現奇偶校驗錯誤)信號。

Onboard DRAM

The DRAM is accessible by the MC68030, PCC, LANCE, and

VMEbus. It is specifically optimized for the MC68030.

The parity feature is not implemented on the MVME147-010.

The MVME147 has parity check which operates in one of three user

selectable modes.

In mode 1, no parity checking is performed and the DRAM operates

at maximum speed.

In mode 2, parity checking is performed for all bus masters and the

DRAM operates at maximum speed when the MC68030 is bus

master. When a parity error occurs in mode 2 and the MC68030 is

the local bus master, the bus error signal is not activated during the

current cycle. The bus error is activated during all subsequent

MC68030 DRAM cycles. All other bus masters are notified of parity

errors during the current cycle, consequently their DRAM access

time increases by 1 clock.

In mode 3, parity checking is performed for all bus masters and

parity errors are reported during the current cycle. In this mode, the

DRAM access time is extended by one clock cycle to allow for parity

checking.

MC68030 DRAM Accesses

The MC68030 is the default local bus master, therefore it is the local

bus master as long as no other device requests local bus mastership.

PCC DRAM Accesses

When the PCC needs to transfer data, it requests local bus

mastership from the GCC multiport arbiter. When the PCC has

been granted local bus mastership, it executes one bus cycle and

then releases bus mastership. If a parity error is detected during a

PCC to DRAM read cycle, a bus error is returned to the PCC.

Functional DescriptWhen the VMEbus map decoder detects an onboard DRAM select,

the VMEchip requests local bus mastership from the GCC

multiport arbiter. When the GCC multiport arbiter has granted

local bus mastership, a DRAM read or write cycle happens and the

VMEchip activates the DTACK* (or BERR* if parity is enabled and

a parity error occurs) signal on the VMEbus.