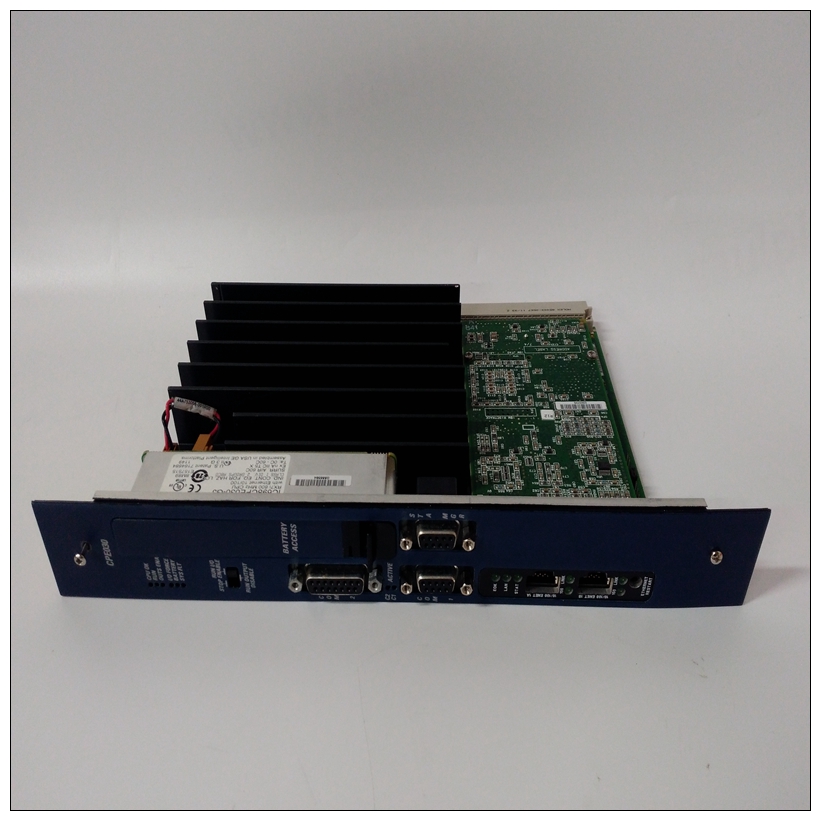

IC698CPE030嵌入式模塊,GE中文PDF說明書在線閱讀

這些位對LAN芯片生成的中斷級別進(jìn)行編程。級別0不生成中斷。位3當(dāng)該位為高位時,中斷被啟用。中斷是此位低時禁用。位7當(dāng)該位為高位時,在以下位置生成LAN端口中斷:以位0-2編程的電平。該位是電平敏感的,并且當(dāng)中斷啟用和LAN中斷激活時激活。當(dāng)本地發(fā)生奇偶校驗錯誤時,設(shè)置該位處理器正在訪問RAM。

IC698CPE030嵌入式模塊通過將1寫入它該位通過重置清除。位1該位在通電復(fù)位時設(shè)置。它被清除給它寫一個1。安裝MVME147BUG后,其初始化代碼清除該位。位設(shè)置和清除指令不應(yīng)用于此控制寄存器。因為中斷被寫入1到狀態(tài)位,狀態(tài)位為1到指示掛起的中斷,讀-修改-寫序列可能清除掛起的中斷。這些位編程SCSI端口生成的中斷級別。級別0不生成中斷。這些位通過重置。位3當(dāng)該位為高位時,中斷被啟用。中斷是此位低時禁用。該位通過重置清除。位4該位用于控制SCSI總線上的重置信號。什么時候該位較低,SCSI重置信號不由MVME147驅(qū)動。當(dāng)該位高時,SCSI重置由MVME147驅(qū)動。該位通過重置清除。位5該位表示SCSI重置信號的狀態(tài)。當(dāng)這個位低,則SCSI重置信號未激活。當(dāng)該位較高時,SCSI重置信號處于活動狀態(tài)。位6當(dāng)該位為高位時,將在以下位置生成SCSI重置中斷:以位0-2編程的電平。該位是邊緣敏感的,并且設(shè)置在中斷啟用和SCSI重置的前沿。寫入1或中斷時,該位被清除已禁用。清除后,它將保持清除狀態(tài),直到下一個中斷啟用和SCSI重置的前沿。這一位是通過重置清除。位7當(dāng)該位為高位時,SCSI端口中斷在以位0-2編程的電平。該位是位6和的ORSCSI芯片中斷。該位通過重置清除。

These bits program the interrupt level the LAN chip generates.

Level 0 does not generate an interrupt.

Bit 3 When this bit is high, the interrupt is enabled. The interrupt is

disabled when this bit is low.

Bit 7 When this bit is high, a LAN port interrupt is being generated at

the level programmed in bits 0-2. This bit is level sensitive and it

is active when interrupt enable and LAN interrupt are active. This bit is set when a parity error occurs while the local

processor is accessing RAM. This bit is cleared by writing a 1 to

it. This bit is cleared by reset.

Bit 1 This bit is set when a power-up reset occurs. It is cleared by

writing a 1 to it. When the MVME147BUG is installed, its

initialization code clears this bit. Bit set and clear instructions should not be used on this

control register. Because the interrupt is cleared by

writing a 1 to status bit and the status bit is a 1 to

indicate a pending interrupt, the read-modify-write

sequence may clear a pending interrupt. These bits program the interrupt level the SCSI port generates.

Level 0 does not generate an interrupt. These bits are cleared by

reset.

Bit 3 When this bit is high, the interrupt is enabled. The interrupt is

disabled when this bit is low. This bit is cleared by reset.

Bit 4 This bit is used to control the reset signal on the SCSI bus. When

this bit is low, the SCSI reset signal is not driven by MVME147.

When this bit is high, the SCSI reset is driven by MVME147.

This bit is cleared by reset.

Bit 5 This bit indicates the state of the SCSI reset signal. When this bit

is low, the SCSI reset signal is not active. When this bit is high,

the SCSI reset signal is active.

Bit 6 When this bit is high, a SCSI reset interrupt is being generated at

the level programmed in bits 0-2. This bit is edge sensitive and it

is set on the leading edge of interrupt enable and SCSI reset.

This bit is cleared when a 1 is written to it or when the interrupt

is disabled. When cleared, it remains cleared until the next

leading edge of interrupt enable and SCSI reset. This bit is

cleared by reset.

Bit 7 When this bit is high, a SCSI port interrupt is being generated at

the level programmed in bits 0-2. This bit is the OR of bit 6 and

the SCSI chip interrupt. This bit is cleared by reset.