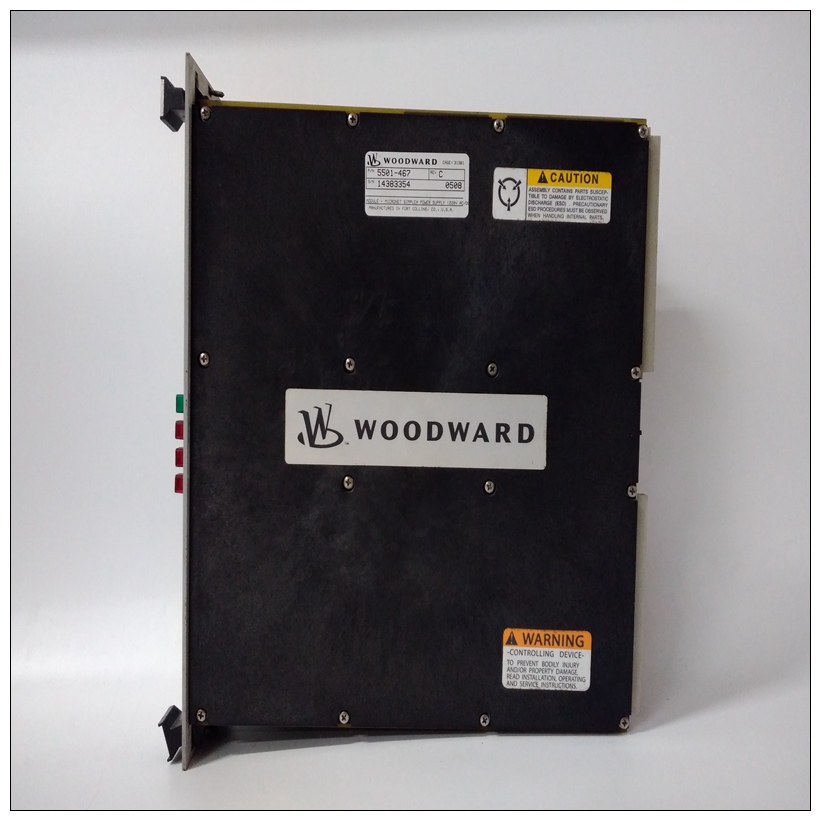

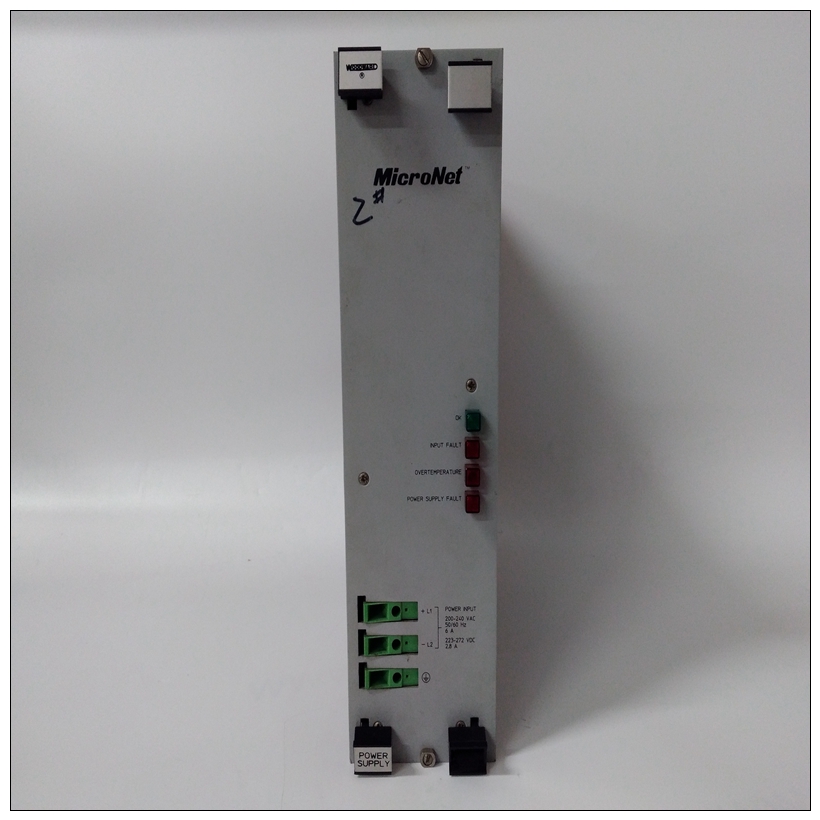

WOODWARD 5501-467數字調節器,5501-467使用區域

MVME162提供1MB、4MB和8MB DRAM選項。DRAM架構對于1MB是非交織的,對于4MB和8MB是交織的。當發生以下情況時,可以在中斷或總線異常的情況下啟用奇偶校驗保護:檢測到奇偶校驗錯誤。DRAM性能在DRAM內存控制器在MCchip編程模型中的應用MVME162嵌入式控制器程序員參考指南。DRAM地圖解碼器可以編程以適應不同的基礎夾層板的地址和尺寸。車載DRAM已禁用通過本地總線重置,并且必須在DRAM可以已訪問。

WOODWARD 5501-467數字調節器請參閱MVME162嵌入式中的MCchip說明詳細編程信息的控制器程序員參考指南。大多數DRAM設備在DRAM之前需要一定數量的訪問周期完全可操作。通常,車載刷新可以滿足此要求電路和正常DRAM初始化。然而,軟件應該確保對每個RAM組執行至少10個初始化周期。電池備份RAM和時鐘MVME162上使用了MK48T08 RAM和時鐘芯片。這個芯片提供時鐘、振蕩器、晶體、電源故障檢測、內存寫保護、8KB RAM和一個28針封裝中的電池。時鐘以BCD 24小時格式提供秒、分鐘、小時、天、日期、月份和年份總體安排28、29(閏年)和30天月的修正為自動生成。時鐘不會產生中斷。雖然MK48T08是一個8位設備,由MCchip提供的接口支持對MK48T08的8位、16位和32位訪問。請參閱MCchip說明第3章和MK48T08數據表中的詳細編程和電池壽命信息。VMEbus接口和VMEchip2可選的VMEchip2提供本地總線到VMEbus和VMEbus到本地總線接口。VMEchip2還可以提供VMEbus系統控制器功能。參考MVME162嵌入式控制器程序員的有關詳細編程信息的參考指南。參考MVME162嵌入式控制器引腳分配支持信息手冊VMEbus背板連接器P1和P2。注意,未使用VMEchip2中的中止開關邏輯。GPI輸入不使用位于$FFF40088位7-0的VMEchip2。這個中止開關中斷集成在位置處的MCchip ASIC中GPI輸入在位置處集成到MCchip ASIC中$FFF4202C,位23-16。輸入/輸出接口MVME162為許多系統應用提供板載輸入/輸出。輸入/輸出功能包括串行端口、工業包(IP)接口和可選LAN以太網收發器和SCSI大容量存儲設備的接口

Onboard DRAM

The MVME162 offers a 1MB, a 4MB, and an 8MB DRAM option. The DRAM

architecture is non-interleaved for 1MB and interleaved for 4MB and 8MB.

Parity protection can be enabled with interrupts or bus exception when a

parity error is detected. DRAM performance is specified in the section on the

DRAM Memory Controller in the MCchip Programming Model in the

MVME162 Embedded Controller Programmer’s Reference Guide.

The DRAM map decoder can be programmed to accommodate different base

address(es) and sizes of mezzanine boards. The onboard DRAM is disabled

by a local bus reset and must be programmed before the DRAM can be

accessed. Refer to the MCchip description in the MVME162 Embedded

Controller Programmer’s Reference Guide for detailed programming information.

Most DRAM devices require some number of access cycles before the DRAMs

are fully operational. Normally this requirement is met by the onboard refresh

circuitry and normal DRAM initialization. However, software should insure

that a minimum of 10 initialization cycles are performed to each bank of RAM.Battery Backed Up RAM and Clock

An MK48T08 RAM and clock chip is used on the MVME162. This chip

provides a time-of-day clock, oscillator, crystal, power fail detection, memory

write protection, 8KB of RAM, and a battery in one 28-pin package. The clock

provides seconds, minutes, hours, day, date, month, and year in BCD 24-hour

format. Corrections for 28-, 29- (leap year), and 30-day months are

automatically made. No interrupts are generated by the clock. Although the

MK48T08 is an 8- bit device, the interface furnished by the MCchip supports

8-, 16-, and 32-bit accesses to the MK48T08. Refer to the MCchip description

in Chapter 3 and to the MK48T08 data sheet for detailed programming and

battery life information.

VMEbus Interface and VMEchip2

The optional VMEchip2 provides the local-bus-to-VMEbus and VMEbus-tolocal-bus interfaces. The VMEchip2 can also provide the VMEbus system

controller functions. Refer to the MVME162 Embedded Controller Programmer’s

Reference Guide for detailed programming information. Refer to the MVME162

Embedded Controller Support Information manual for the pin assignments of

VMEbus backplane connectors P1 and P2.

Note that the ABORT switch logic in the VMEchip2 is not used. The GPI inputs

to the VMEchip2 which are located at $FFF40088 bits 7-0 are not used. The

ABORT switch interrupt is integrated into the MCchip ASIC at location

$FFF42043. The GPI inputs are integrated into the MCchip ASIC at location

$FFF4202C, bits 23-16.

I/O Interfaces

The MVME162 provides onboard I/O for many system applications. The I/O

functions include serial ports, IndustryPack (IP) interfaces, and optional

interfaces for LAN Ethernet transceivers and SCSI mass storage devices