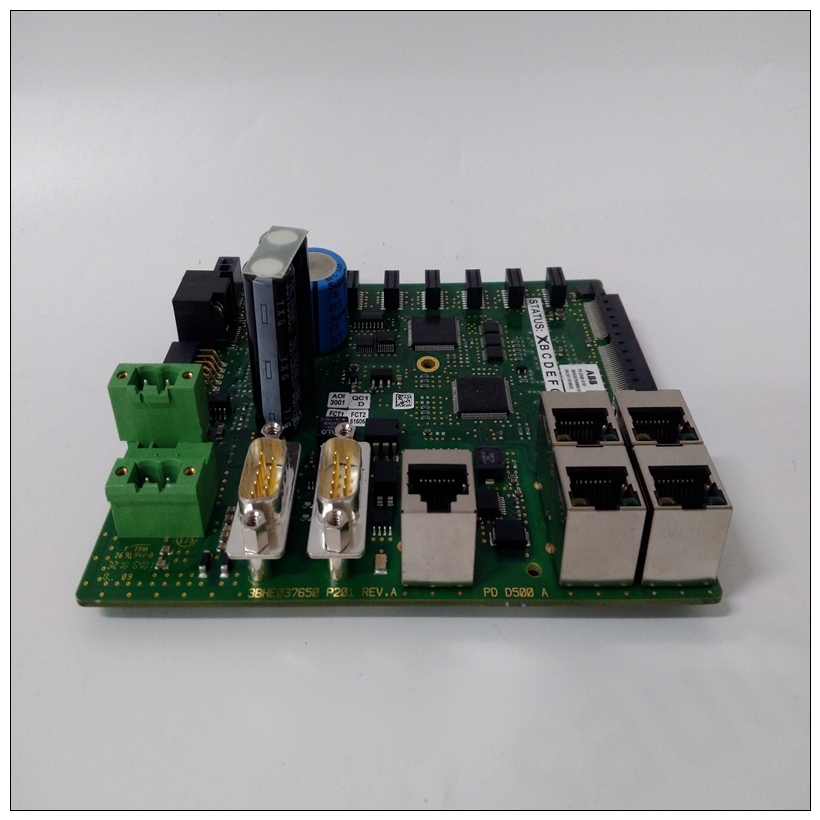

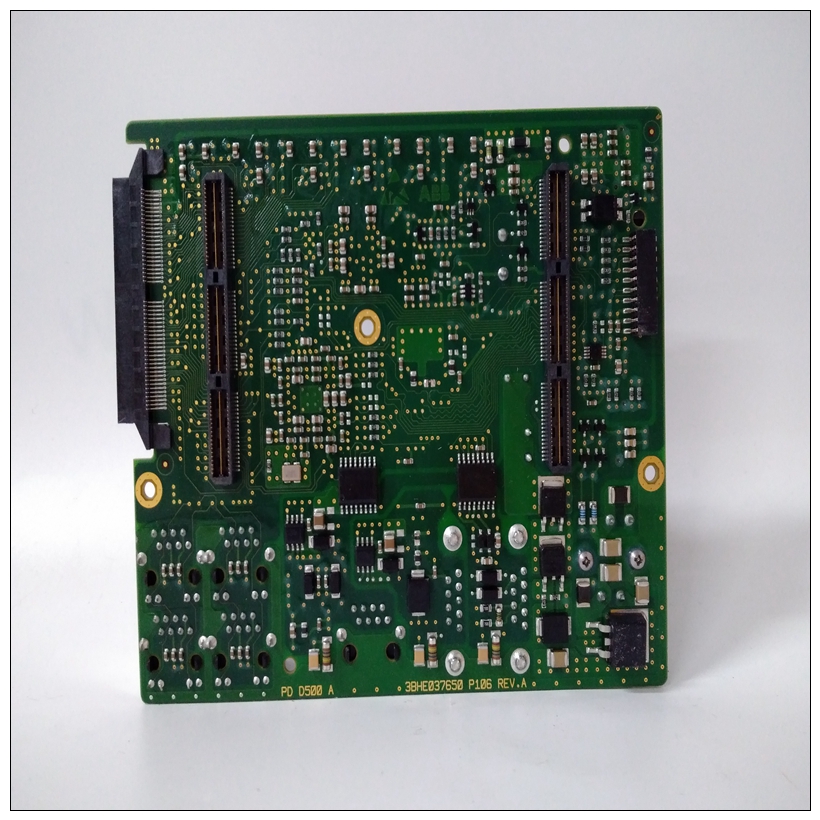

PDD500A101 3BHE037649R0101控制卡,ABB使用配置說明

該寄存器用于啟用VMEchip中斷處理程序來響應特定的實用程序中斷請求。當中斷處理程序檢測到中斷請求時從一個啟用的功能中,它通過請求MC68030啟動中斷確認循環(huán)來響應如果在PCC中設置了主中斷啟用位。所有的該寄存器中的位通過任何重置進行清除。如本節(jié)GCSR編程部分所述第章,GCSR提供兩個全局注意力中斷位:SIGLP和SIGHP,允許其他VMEbus主機以低優(yōu)先級(1級)和高優(yōu)先級中斷MC68030優(yōu)先級(5級)。

PDD500A101 3BHE037649R0101控制卡將SIGLEN控制位設置為1取消掩碼SIGLP中斷。位2,如本節(jié)GCSR編程部分所述第二章,GCSR提供了四個位置監(jiān)視器。其中兩個位置監(jiān)視器0和1在訪問它們配置為監(jiān)視的VMEbus地址。LM0EN控制位允許軟件屏蔽中斷當檢測到對監(jiān)控地址的訪問時請求通過位置監(jiān)視器0。本地中斷級別如所示表4-6。將LM0EN位設置為1將取消屏蔽中斷。位3 VMEchip允許軟件對中斷處理程序進行編程在結束VMEbus IACK后生成本地中斷周期本地中斷的級別如表4-6所示。將IACKEN控制位設置為1啟用IACK中斷。此功能旨在與VMEchip全局中斷功能。如果設置了該位,則本地VMEbus IACK時產(chǎn)生中斷(至MC68030循環(huán)確認中斷(參考中斷請求本章注冊部分)。如本節(jié)GCSR編程部分所述第二章,GCSR提供了四個位置監(jiān)視器。其中兩個位置監(jiān)視器0和1在訪問它們配置為監(jiān)視的VMEbus地址。LM1EN控制位允許軟件屏蔽中斷當檢測到對監(jiān)控地址的訪問時請求通過位置監(jiān)視器1。本地中斷級別如所示表4-6。將LM1EN位設置為1將取消屏蔽中斷。位5,如本節(jié)GCSR編程部分所述第二章,全球氣候變化報告提供了全球高度優(yōu)先關注中斷位SIGHP,允許其他VMEbus主機中斷MC68030。顯示了本地中斷的級別在表4-6中。將SIGNEN控制位設置為1將取消屏蔽SIGHP中斷。位6將SFIEN設置為1啟用VMEbus SYSFAIL上的低電平線路導致MC68030中斷。水平SYSFAIL*中斷如表4-6所示。位7 VMEchip允許軟件配置VMEbus主機在寫投遞模式下操作(即,確認MC68030 VMEbus綁定寫入周期,在實際在VMEbus上執(zhí)行)。如果VMEchip遇到VMEbus總線錯誤,因為它試圖完成寫操作循環(huán)時,VMEchip通過7級中斷通知MC68030,如果

設置WPERREN位。

This register is used to enable the VMEchip interrupt

handler to respond to specific utility interrupt requests.

When the interrupt handler detects an interrupt request

from one of the enabled functions, it responds by requesting the MC68030 to initiate an interrupt acknowledge cycle

if the master interrupt enable bit is set in the PCC. All the

bits in this register are cleared by any reset. As described in the Programming the GCSR section in this

chapter, the GCSR provides two global attention interrupt bits:

SIGLP and SIGHP, which allow other VMEbus masters to

interrupt the MC68030 on a low priority (Level 1) and on a high

priority (Level 5). Setting the SIGLEN control bit to 1 unmasks

the SIGLP interrupt.

Bit 2 As described in the Programming the GCSR section in this

chapter, the GCSR provides four location monitors. Two of

them, location monitor 0 and 1, cause a local interrupt when the

VMEbus address they are configured to monitor is accessed.

The LM0EN control bit allows software to mask the interrupt

requested when an access is detected to the address monitored

by location monitor 0. The level of local interrupt is shown in

Table 4-6. Setting the LM0EN bit to 1 unmasks the interrupt.

Bit 3 The VMEchip allows software to program the interrupt handler

to generate a local interrupt after it concludes a VMEbus IACK

cycle. The level of the local interrupt is shown in Table 4-6.

Setting the IACKEN control bit to 1 enables the IACK interrupt.

This function is intended to be coupled with the use of the

VMEchip global interrupt function. If this bit is set, a local

interrupt (to the MC68030) is generated when a VMEbus IACK

cycle acknowledges the interrupt (refer to the Interrupt Request

Register section in this chapter). As described in the Programming the GCSR section in this

chapter, the GCSR provides four location monitors. Two of

them, location monitor 0 and 1, cause a local interrupt when the

VMEbus address they are configured to monitor is accessed.

The LM1EN control bit allows software to mask the interrupt

requested when an access is detected to the address monitored

by location monitor 1. The level of local interrupt is shown in

Table 4-6. Setting the LM1EN bit to 1 unmasks the interrupt.

Bit 5 As described in the Programming the GCSR section in this

chapter, the GCSR provides a global high priority attention

interrupt bit SIGHP which allows other VMEbus masters to

interrupt the MC68030. The level of the local interrupt is shown

in Table 4-6. Setting the SIGHEN control bit to 1 unmasks the

SIGHP interrupt.

Bit 6 Setting SFIEN to 1 enables a low level on the VMEbus SYSFAIL*

line to cause an interrupt to the MC68030. The level of the

SYSFAIL* interrupt is shown in Table 4-6.

Bit 7 The VMEchip allows software to configure the VMEbus master

to operate in a write posted mode (i.e., acknowledge the

MC68030 VMEbus bound write cycle before it has actually been

executed on the VMEbus). If the VMEchip encounters a

VMEbus bus error as it attempts to complete the write posted

cycle, the VMEchip notifies the MC68030 via Level 7 interrupt if

the WPERREN bit is set.