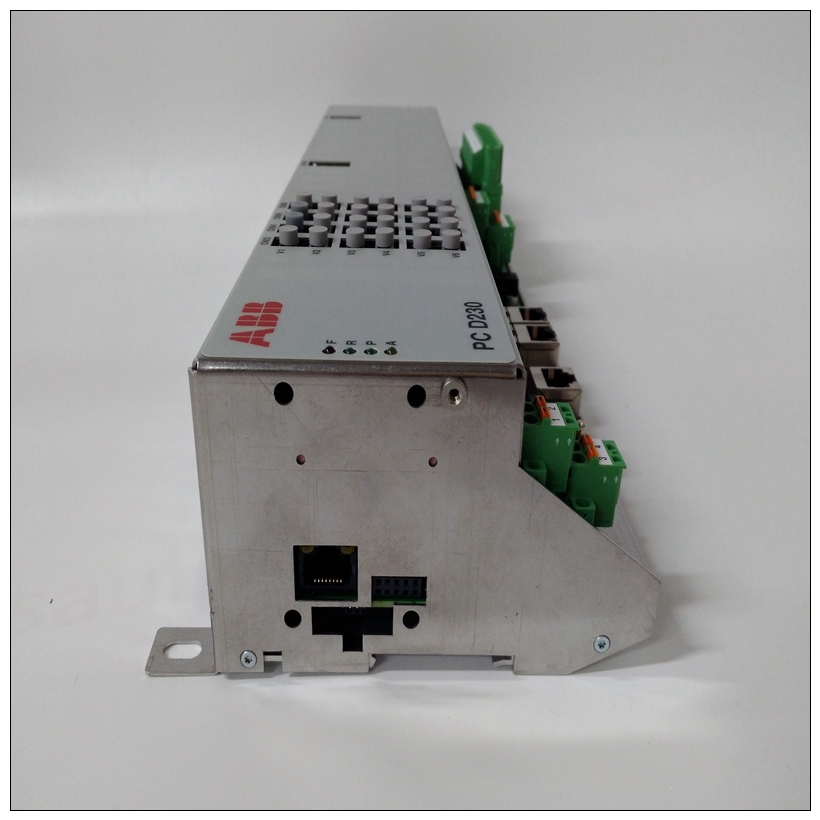

PCD230A 3BHE022291R0101控制卡件,ABB配置教程

RWD位允許軟件配置請(qǐng)求者版本模式設(shè)置位時(shí),如果RNEVER和DWB都是清除為0時(shí),請(qǐng)求者在MC68030完成VMEbus循環(huán)。當(dāng)位被清除時(shí),如果RNEVER和DWB都被清除為0,請(qǐng)求者操作在請(qǐng)求發(fā)布(ROR)模式下。獲得控制權(quán)后在VMEbus中,它保持控制,直到檢測(cè)到另一個(gè)請(qǐng)求在VMEbus上掛起。該位通過(guò)任何重置清除。位5 RONR位控制VMEchip的方式請(qǐng)求VMEbus。當(dāng)設(shè)置位時(shí);任何時(shí)候MVME147擁有總線主控權(quán)

PCD230A 3BHE022291R0101控制卡件,然后放棄了VMEchip在檢測(cè)到總線之前,不會(huì)再次請(qǐng)求VMEbus請(qǐng)求信號(hào)BR*在其電平上被否定至少150納秒。當(dāng)VMEchip檢測(cè)到BR*否定時(shí),它會(huì)抑制再次駕駛至少200 ns。該位通過(guò)任何重置清除。位6當(dāng)MVME147為VMEbus主機(jī)時(shí),DHB狀態(tài)位為1否則為0。位7將DWB控制位設(shè)置為1會(huì)導(dǎo)致VMEchip請(qǐng)求

VMEbus(如果還沒有總線主控)。當(dāng)VMEbus主控權(quán)已經(jīng)獲得,直到之后才放棄DWB和RNEVER位均被清除。此位已清除通過(guò)任何重置。設(shè)置MASD16位迫使MVME147僅執(zhí)行VMEbus上的D8和D16數(shù)據(jù)傳輸。清除MASD16位允許在當(dāng)MC68030在以下范圍內(nèi)訪問時(shí)的VMEbus$F0000000。(對(duì)高于$F0000000的VMEbus位置的訪問是無(wú)論MASD16位如何,始終限制為D8/D16。)該位由SYSRESET清除。位1,如果設(shè)置了MASA24位,或MC68030訪問VMEbus在低于1000000美元的范圍內(nèi),主驅(qū)動(dòng)器驅(qū)動(dòng)其中一個(gè)VMEbus期間的標(biāo)準(zhǔn)(24位)地址修飾符代碼周期(除非主機(jī)配置為使用主機(jī)地址主地址修飾符中描述的修飾符寄存器本章注冊(cè)部分)。具體標(biāo)準(zhǔn)AM代碼由MC68030在循環(huán)期間的三個(gè)功能代碼行,如表所示在下面該位由SYSRESET清除。位2,如果設(shè)置了MASA16位,或MC68030訪問高于$FFFF0000的VMEbus,短(16位)AM無(wú)論MASA24位的狀態(tài)如何(除非主機(jī)配置為使用主機(jī)地址修飾符寄存器如主地址修改器寄存器中所述本章第節(jié))。具體的短AM代碼為根據(jù)MC68030在循環(huán)期間有三個(gè)功能代碼行,如下表。該位由SYSRESET清除。

The RWD bit allows software to configure the requester release

mode. When the bit is set, if RNEVER and DWB are both

cleared to 0, the requester releases the VMEbus after the

MC68030 completes a VMEbus cycle. When the bit is cleared, if

RNEVER and DWB are both cleared to 0, the requester operates

in the Release-On-Request (ROR) mode. After acquiring control

of the VMEbus, it maintains control until it detects another

request pending on the VMEbus. This bit is cleared by any reset.

Bit 5 The RONR bit controls the manner in which the VMEchip

requests the VMEbus. When the bit is set; anytime the

MVME147 has bus mastership, then gives it up, the VMEchip

does not request the VMEbus again until it detects the bus

request signal BR*, on its level, negated for at least 150 ns.

When the VMEchip detects BR* negated, it refrains from

driving it again for at least 200 ns.

This bit is cleared by any reset.

Bit 6 The DHB status bit is 1 when the MVME147 is VMEbus master

and 0 when it is not.

Bit 7 Setting the DWB control bit to 1 causes the VMEchip to request

the VMEbus (if not already bus master). When VMEbus

mastership has been obtained, it is not relinquished until after

the DWB and RNEVER bits are both cleared. This bit is cleared

by any reset.Setting the MASD16 bit forces the MVME147 to perform only

D8 and D16 data transfers on the VMEbus. Clearing the

MASD16 bit allows D8, D16, and D32 transfer capability on the

VMEbus when the MC68030 accesses in the range below

$F0000000. (Accesses to VMEbus locations above $F0000000 are

always restricted to D8/D16 regardless of the MASD16 bit.)

This bit is cleared by SYSRESET.

Bit 1 If either the MASA24 bit is set, or the MC68030 accesses the

VMEbus in the range below $1000000, the master drives one of

the standard (24-bit) address modifier codes during VMEbus

cycles (unless the master is configured to use the master address

modifier register as described in the Master Address Modifier

Register section in this chapter). The specific standard AM code

is determined from the levels that the MC68030 drives on the

three function code lines during the cycle, as shown in the table

below. This bit is cleared by SYSRESET.