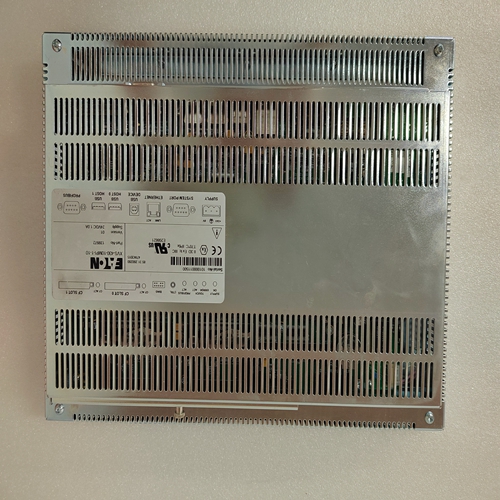

EATON XVS-430-10MPI-1-10觸摸屏

應用變量放在網段上的一組應用程序數據,可將其分組在一起在通信變量(COMV)中。協會

在網絡配置工具中的設備配置之間創建的鏈接

以及硬件配置工具中描述的機架系統。

總線仲裁器

在每個FIP網絡中,一個或多個FIP設備必須充當總線仲裁器。這個

總線仲裁器是控制FIP網絡訪問的設備。沒有公共汽車

仲裁器:在FIP網絡上不能交換數據。

總線接口單元

DIN導軌安裝單元,將現場控制I/O模塊連接至FIP總線。

總線控制器

FIP總線控制器是一個安裝在機架上的PLC模塊,將PLC連接到

FIP總線或總線。總線控制器狀態位

總線控制器、網絡和PLC參考表中的80位狀態區域

信道狀態數據。該狀態區域的位置在硬件期間分配

總線控制器的配置。

總線掃描

FIP總線掃描涉及FIP宏周期的恒定重復。FIP

宏循環由FIP總線仲裁器執行。90-70系列FIP總線控制器

可以是FIP網絡中的潛在總線仲裁器。宏循環由

基于遠程設備配置的配置軟件及其

相關的I/O模塊和其他用戶輸入。

信道狀態位

信道狀態位是總線控制器狀態位的位17-80。他們組成

32個潛在通信中的每一個的錯誤位和數據傳輸位

可以建立的信道。COMREQ

“通信請求”可包含在90-70系列PLC。定義了許多不同類型的COMREQ

90-70系列PLC。一些COMREQ可用于從PLC發送命令

CPU連接到FIP總線控制器。

COMREQ命令塊

此結構包含有關要執行的FIP命令的信息。COMREQ狀態字

系列90-70存儲器中的選定區域,其中COMREQ的結果為:放置。

Application Variable

Set of application data put on the network segment which may be grouped together

in communication variables (COMVs).

Association

A link created between a device configuration in the Network Configuration Tool

and a rack system described in the Hardware Configuration Tool.

Bus Arbiter

In every FIP Network, one or more of the FIP devices must act as Bus Arbiter. The

Bus Arbiter is the device that controls access to the FIP Network. Without a Bus

Arbiter no data can be exchanged on a FIP Network.

Bus Interface Unit

A DIN-rail mounted unit that interfaces Field Control I/O modules to a FIP bus.

Bus Controller

The FIP Bus Controller is a rack-mounted PLC module that interfaces the PLC to a

FIP bus or busses.Bus Controller Status Bits

An 80-bit status area in the PLC reference table for Bus Controller, network, and

channel status data. The location of this status area is assigned during hardware

configuration of the Bus Controller.

Bus Scan

The FIP Bus Scan involves the constant repetition of the FIP macrocycle. The FIP

macrocycle is executed by the FIP Bus Arbiter. The Series 90-70 FIP Bus Controller

may be a potential Bus Arbiter in a FIP network. The macrocycle is generated by the

configuration software based on the configuration of the remote devices and their

associated I/O modules, and other user input.

Channel Status Bits

The Channel Status bits are bits 17-80 of the Bus Controller Status Bits. They consist

of an error bit and a data transfer bit for each of the 32 potential communications

channels that can be established.

COMREQ

A “Communications Request” that can be included in the application program of the

Series 90-70 PLC. Many different types of COMREQs have been defined for the

Series 90-70 PLC. Some COMREQs can be used to send commands from the PLC

CPU to the FIP Bus Controller.

COMREQ Command Block

This structure contains information about the FIP command to be executed.

COMREQ Status Word

A selected area in Series 90-70 memory where the results of the COMREQ are

placed.