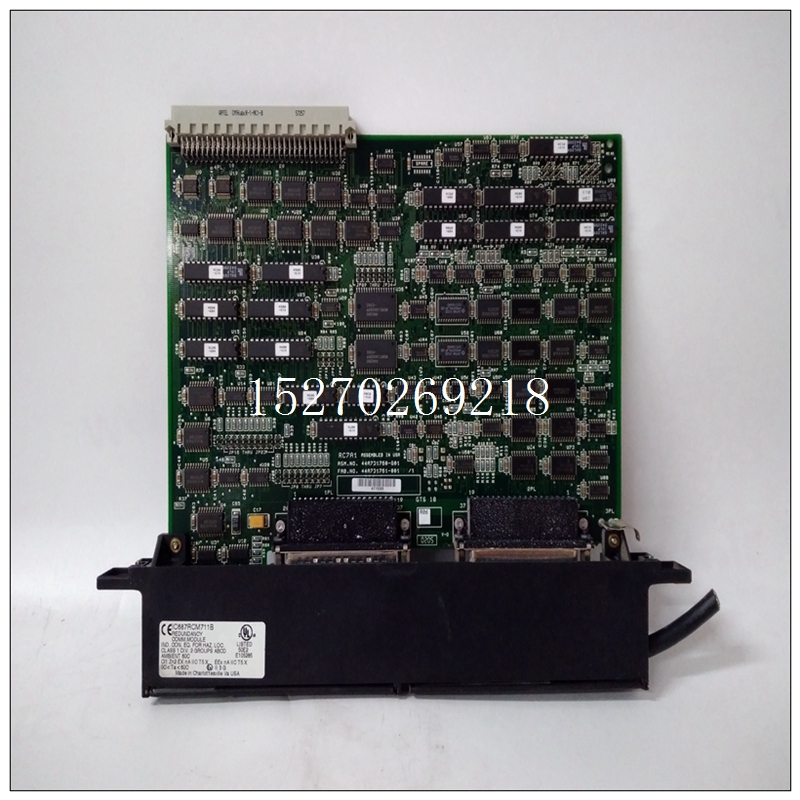

IC687RCM711B使用過程,GE燃機卡

改進的高頻抑制選項,則J2為已安裝,不應移除。所有RFILT輸入SIP將被占用具有SIP標頭。這些是0的SIP電阻器?. J1可能已安裝,但未安裝必需的這些SIP為輸入源提供VME接地參考。隔離輸入源(如3V/5V輸入模塊)需要這種配置防止高頻噪聲成為共模信號導致輸出數據波動。

5.4.3.2輸入電壓范圍輸入電壓范圍由跳線J4-1、2、3控制。最大滿負荷標度范圍為20 V。要將滿標度范圍修改為10 V,請配置跳線如表5.3-1所示。所有輸入電壓必須在VMEbus的12 V范圍內線性操作的地面。對于“一”以外的增益,所有輸入電壓必須為VMEbus接地10 V以內。對于單端操作,接地感應計為輸入。

IC687RCM711B使用過程5.4.3.3雙極或單極操作模擬輸入的雙極或單極操作通過跳線J3-1、2、3如表5.3-1所示。5.4.4外部觸發跳線說明外部觸發電路允許用戶輸入TTL電平“零”至啟動A/D轉換或A/D轉換掃描序列。此輸入必須為通過安裝跳線J9和J10啟用PC連接器。J9允許接地參考連接。J10啟用觸發信號,并標記為EXT STRT在示意圖上轉換L(SH6)。除了跳投,ENA EXT STRT必須在控制寄存器中設置H(D11)。該信號也被帶到用戶通過P2連接器。外部電路可以監測該TTL信號,當其高達邏輯“1”時,電路板已準備好進行下一個STRT轉換輸入以開始轉換。表5.4.4-1給出了外部觸發信號。內部定時器-16、32或48位定時器選擇內部定時器(8254)有三個16位計數器。這三個計時器可以通過跳線生成16、32或48的最大計數長度位(請參閱第4.4.6節以確定計數器分辨率和編程)。表5.4.5-1顯示了可能的跳線配置。A/D掃描序列長度跳線配置三種掃描模式(自動掃描模式、掃描輪詢模式、掃描中斷模式)使用J6處的跳線確定掃描多少通道。掃描始終從通道0開始,然后繼續使用下一個更高的通道,直到J6與通道總數匹配已掃描。例如,出廠設置通過以下方式執行所有64個通道(0到63)在J6中編碼64。J6-1是最高有效位。J6-7是最低有效位。J6-1、J6-2、J6-3、J6-4、J6-5、J6-6、J6-7的權重為64、32、16、8、4、2和1通道。安裝的跳線表示“零”。表5.4.6-1給出了針對不同掃描長度安裝跳線的一些示例。看見第3.6.1節了解跳線設置的限制

Frequency Rejection option is ordered, J2 is

installed and should NOT be removed. All of the RFILT input SIPs will be occupied

with SIP headers. These are SIP resistors of 0 ?. J1 may be installed but it is not

necessary. These SIPs supply the input source with the VME ground reference.

Isolated input sources, such as the 3V/5V input modules, require this configuration

to prevent high frequency noise from becoming a common mode signal and

causing fluctuations in the output data.

5.4.3.2 Input Voltage Range

Input voltage range is controlled by jumpers J4-1, 2, 3. The maximum full

scale range is 20 V. To modify the full scale range to 10 V configure the jumpers

as indicated in Table 5.3-1. All input voltages must be within 12 V of VMEbus

ground for linear operation. For gains other than "one", all input voltages must be

within 10 V of VMEbus ground. For single-ended operation, the ground sense

counts as an input.

5.4.3.3 Bipolar or Unipolar Operation

Bipolar or unipolar operation of the analog inputs is selected with

jumpers J3-1, 2, 3 as indicated in Table 5.3-1.

5.4.4 External Trigger Jumper Description

The external trigger circuitry allows the user to input a TTL level "zero" to

start an A/D conversion or an A/D conversion scan sequence. This input must be

enabled to the PC connector by installing jumpers J9 and J10. J9 allows a ground

reference connection. J10 enables the trigger signal and is labeled EXT STRT

CONVERT L on the schematic (SH6). In addition to the jumper, the ENA EXT STRT

H (D11) must be set in the control register. This signal is also brought out to the

user via the P2 connector. External circuitry can monitor this TTL signal, and when it goes High to a logic "one" then the board is ready for the EXT STRT CONVERT L

input to begin a conversion(s). Table 5.4.4-1 gives the connector description for the

External Trigger signal.

Internal Timer - 16-, 32-, or 48-Bit Timer Selection

The internal timer (8254) has three 16-bit counters. These three timers

may be jumpered in a way to generate a maximum count length of 16, 32, or 48

bits (refer to Section 4.4.6 to determine counter resolution and programming).

Table 5.4.5-1 shows the possible jumper configurations. A/D Scan Sequence Length Jumper Configuration

The three scanning modes (AUTO SCANNING MODE, SCANNING

POLL MODE, SCANNING INTERRUPT MODE) use the jumpers at J6 to determine

how many channels to scan. Scans always begin with Channel 0 and continue

with the next higher channel until J6 matches the total number of channels

scanned. For example, the factory setting does all 64 channels (0 through 63) by

encoding 64 in J6. J6-1 is the most significant bit. J6-7 is the least significant bit.

J6-1, J6-2, J6-3, J6-4, J6-5, J6-6, J6-7 have weights of 64, 32, 16, 8, 4, 2, and 1

channels, respectively. An installed jumper signifies a "zero". Table 5.4.6-1 gives

some examples of the jumpers to be installed for different scan lengths. See

Section 3.6.1 for restrictions on jumper settings.