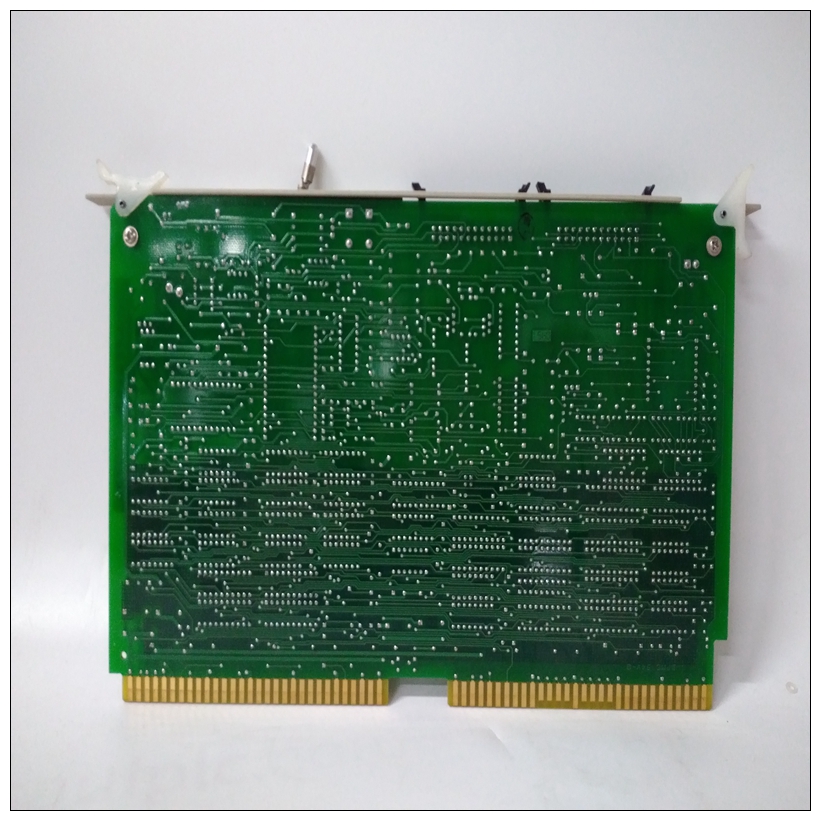

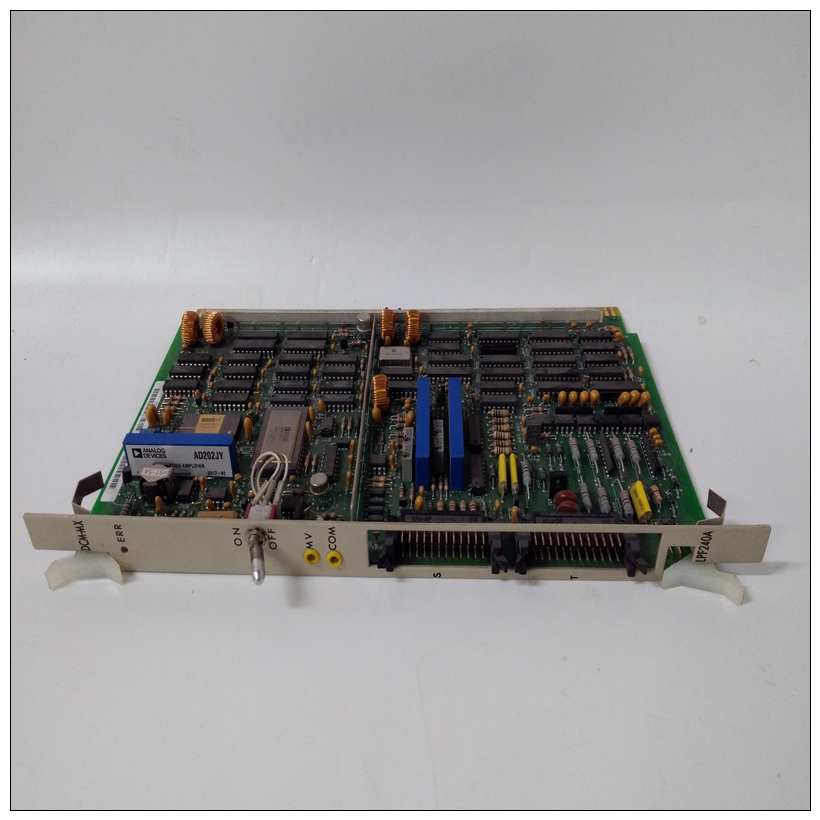

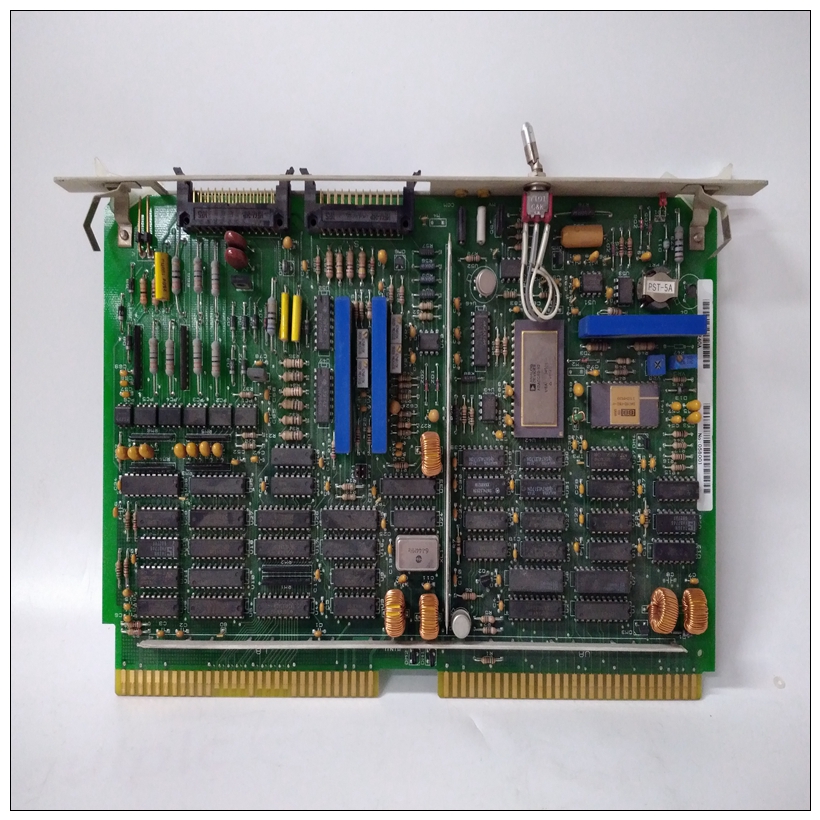

LPF240A工控卡件,HITACHI使用過程

網絡引導控制模塊的“控制”能力需要與將所有必要的模塊(功能)放在一起,并對引導進行排序過程引導序列包括兩個階段:第一階段標記為“地址確定和引導文件選擇”,第二階段標記為“文件傳輸”。第一階段將利用RARP/BOOTP功能和第二階段將利用TFTP能力。網絡輸入/輸出錯誤代碼如果嘗試的網絡操作失敗,197Bug將返回錯誤代碼不成功的多處理器支持MVME197LE雙端口RAM功能使共享RAM可用于遠程處理器以及本地處理器。

LPF240A工控卡件這可以通過以下方式實現:以下兩種方法之一。任何一種方法都可以通過ENV命令作為其遠程啟動開關方法(參考附錄A)。多處理機控制寄存器(MPCR)方法遠程處理器可以在本地MVME197LE中啟動程序執行雙端口RAM,通過使用多處理器發出遠程GO命令控制寄存器(MPCR)。MPCR位于3000美元的共享RAM位置從調試器加載它的基址的偏移量,包含兩個用于控制處理器之間通信的文字。MPCR內容組織如下:多處理器地址寄存器(MPAR),位于共享RAM中調試器加載它的基址的3004美元偏移量的位置,包含兩個字中的第二個字,用于控制處理器之間的通信。MPAR內容指定遠程執行的地址如果MPCR包含G或B,則處理器開始。MPAR組織為通電后,調試監視器自檢例程初始化RAM,包括用于多處理器支持的內存位置。MPCR在通電時包含$00,表示尚未初始化完成隨著初始化的進行,執行路徑到達“提示”例程。在發送提示之前,此例程在MPCR指示初始化完成。然后發送提示。如果沒有終端連接到端口,則仍會輪詢MPCR以查看是否外部處理器需要將控制傳遞給雙端口RAM。如果a終端沒有響應,MPCR被輪詢用于相同的目的,而正在輪詢串行端口以供用戶輸入。

Network Boot Control Module

The “control” capability of the Network Boot Control Module is needed to tie

together all the necessary modules (capabilities) and to sequence the booting

process. The booting sequence consists of two phases: the first phase is labeled

“address determination and bootfile selection” and the second phase is labeled

“file transfer”. The first phase will utilize the RARP/BOOTP capability and the

second phase will utilize the TFTP capability.

Network I/O Error Codes

197Bug returns an error code if an attempted network operation is

unsuccessful.

Multiprocessor Support

The MVME197LE dual-port RAM feature makes the shared RAM available to

remote processors as well as to the local processor. This can be done by either

of the following two methods. Either method can be enabled/disabled by the

ENV command as its Remote Start Switch Method (refer to Appendix A).

Multiprocessor Control Register (MPCR) Method

A remote processor can initiate program execution in the local MVME197LE

dual-port RAM by issuing a remote GO command using the Multiprocessor

Control Register (MPCR). The MPCR, located at shared RAM location of $3000

offset from the base address the debugger loads it at, contains one of two

words used to control communication between processors. The MPCR

contents are organized as follows:The Multiprocessor Address Register (MPAR), located in shared RAM

location of $3004 offset from the base address the debugger loads it at, contains

the second of two words used to control communication between processors.

The MPAR contents specify the address at which execution for the remote

processor is to begin if the MPCR contains a G or B. The MPAR is organized as

followsAt power up, the debug monitor self-test routines initialize RAM, including

the memory locations used for multi-processor support ($3000 through $3007).

The MPCR contains $00 at power-up, indicating that initialization is not yet

complete. As the initialization proceeds, the execution path comes to the

“prompt” routine. Before sending the prompt, this routine places an R in the

MPCR to indicate that initialization is complete. Then the prompt is sent.

If no terminal is connected to the port, the MPCR is still polled to see whether

an external processor requires control to be passed to the dual-port RAM. If a

terminal does respond, the MPCR is polled for the same purpose while the

serial port is being polled for user input.